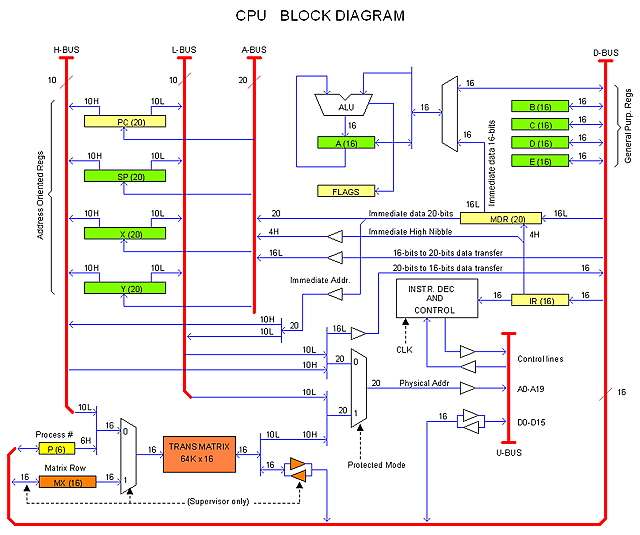

CPU ArchitectureThe figure below describes the Heritage/1 CPU architecture to the block level. I will explain how it works later. For now, you are invited to read my Notes. Remember that this design is in progress.

Registers

16-bits registers (Data oriented):

A Accumulator (Right operand and result for ALU operations)

B General purpose

C General purpose

D General purpose

E General purpose

20-bits Registers (Address oriented):

PC Program Counter (not directly addressable)

SP Stack Pointer (also a gernal purpose 20-bits register)

X Pointer for Indirect Address (also a gernal purpose 20-bits register)

Y Pointer for Indirect Address (also a gernal purpose 20-bits register)

Hidden Registers:

IR (16 bits) Instruction register

MDR (20 bits) Operand holder (both 16 and 20 bits)

FLAGS (?) Status flags

Supervisor Registers (Avilable in Real Mode. Also available for Supervisor code in Protected Mode):

P (6 bits) Current process when in Protected Mode.

MX (16 bits) Trans Matrix address

|

Homebuilt CPUs WebRing

JavaScript by Qirien Dhaela

Join the ring?

David Brooks, the designer of the Simplex-III homebrew computer, has founded the Homebuilt CPUs Web Ring. To join, drop David a line, mentioning your page's URL. He will then add it to the list.

You will need to copy this code fragment into your page.

Project start date: May 13 of 2009

|