RegistersThe CPU has the following (16-bits) registers accessible to the programmer:

General Purpose: B, C, D, E

Special Purpose : Accumulator (A), Program Counter (PC), Stack Pointer (SP), Operand Reg (OR).

The Operand Register (OR) is not thought for programmer's use; however, it is possible (though not recommended) to access it using some "tricks". The mission of the OR register is to read the operand in it during the fetch cycle so it can be available during the exec cycle.

There is also a (6-bits) flags registers (F) to hold the following conditional status:

Z zero

N negative

C carry

V overflow

It also holds the Interrupt Enabled (IE) and Timer Enable (TE) conditions.

The flags register is NOT directly available to programmers. The conditional status is only accesible via conditional branch instructions. Flags IE is accessible via instructions EI, DI.

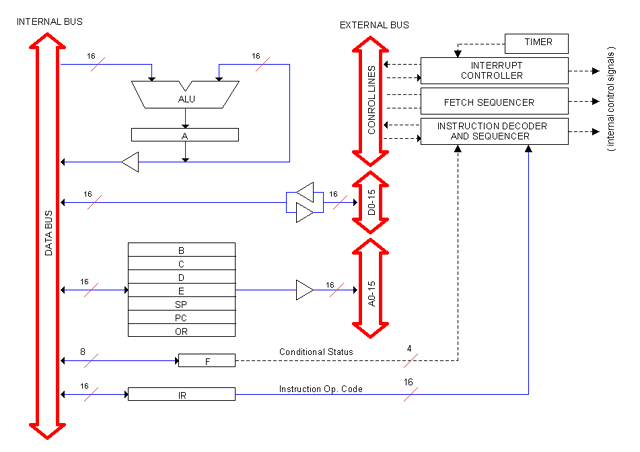

Below is a simplified block diagram of the CPU.

Notice that register A is the only destination for ALU results. Also note that all other registers are double-buffered so they can point to memory by supplying an address directly to the ADDRESS BUS.

|

Homebuilt CPUs WebRing

JavaScript by Qirien Dhaela

Join the ring?

David Brooks, the designer of the Simplex-III homebrew computer, has founded the Homebuilt CPUs Web Ring. To join, drop David a line, mentioning your page's URL. He will then add it to the list.

You will need to copy this code fragment into your page.

Project start date: May 13 of 2009

|