OverviewHeritage/1 is (or will be) a home-brew minicomputer made out of discrete MSI/SSI HCMOS chips and PLDs. It is designed to provide hardware support for Virtual Memory and Multi-Tasking. This book contains overall information about the project.

The Computer

Main Features

Computer Name : Heritage/1

Data Bus : 16 bits

Address Bus : 20 bits (addresses point to 16 bit words)

Main Memory : SRAM 1 Mw (2 MB) max.

Arithmetic : Signed integer (two's complement)

Inst. decode method : Hard-wired logic using PLD chips

Operating Modes : Step, Real, Protected

Virtual Memory : Paging with Pages Tables in SRAM "Matrix" separate from Main Memory.

Page Frame size : 1Kw (2 KB)

Multitasking : Hardware support for up to 64 processes running in separate time-slices.

Software : None (Expected: Some Open Source Operating System)

Peripherals : Memory mapped

Interrupts : Vectored 256 max.

Nested ISR : Yes, based on priority

DMA : Yes

Technology : SSI/MSI HCMOS chips and PLDs

Construction : Prototyping boards with wires soldered (no wire-wrap) housing in 19" rackmount multi-card frames

Clock Speed : Pendig decision (expected: 12 MHz)

Computer Architecture

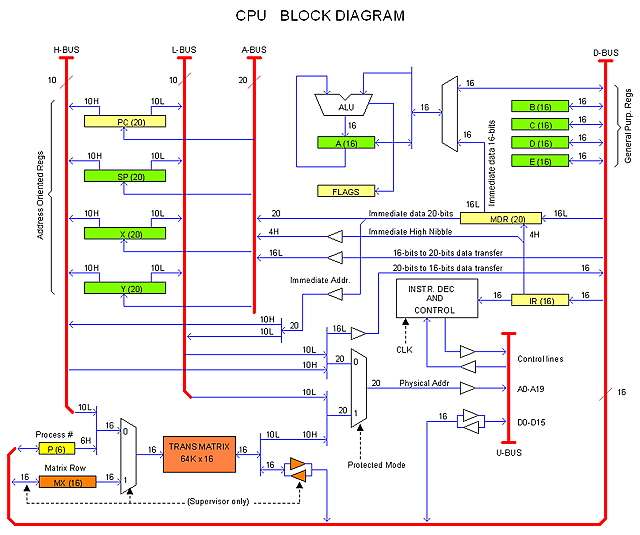

CPU Architecture CPU Architecture

The figure below describes the Heritage/1 CPU architecture to the block level. I will explain how it works later. For now, you are invited to read my Notes. Remember that this design is in progress.

Registers Registers

16-bits registers (Data oriented):

A Accumulator (Right operand and result for ALU operations)

B General purpose

C General purpose

D General purpose

E General purpose

20-bits Registers (Address oriented):

PC Program Counter (not directly addressable)

SP Stack Pointer (also a gernal purpose 20-bits register)

X Pointer for Indirect Address (also a gernal purpose 20-bits register)

Y Pointer for Indirect Address (also a gernal purpose 20-bits register)

Hidden Registers:

IR (16 bits) Instruction register

MDR (20 bits) Operand holder (both 16 and 20 bits)

FLAGS (?) Status flags

Supervisor Registers (Avilable in Real Mode. Also available for Supervisor code in Protected Mode):

P (6 bits) Current process when in Protected Mode.

MX (16 bits) Trans Matrix address

Important Note

This project is currenly on hold. I found that before continuing with a complex design such as that of Heritage/1, it would be better to start a simpler "pre-project" in which I could gain experience with basic Computer Design matters.

The info for the "pre-project" (currently in progress) is in the book titled PREHER-816.

The Project

Main Objective

The goal of this project is to design and build a minicomputer out of discrete components. The challenge is into provide sufficient hardware support for a true (Open Source) operating system than eventually could be ported in a further step.

Porting an operating system so it can run on a proprietary platform is a project per se for which I have no knowledge, no experience. So this is essentially self-educational project. Learning through research and experience in intimate proximity with all implementation details is actually the main objective of this computer project.

Current Status

06/11/2009

The project is officially on hold until I've gained sufficient experience while designing and building the "pre-computer" termed PREHER/816.

Project breakdown

I have broken the project into the following phases. I have not set dead lines because nobody if watting for it, but I can guess it will take quite a long time (one year at least).

Phase 1: Research Phase 1: Research

Start Date: 05/15/2009

I am thinking of a machine capable of running existing open source software on top of a ported UNIX-like kernel, but this may change. During this period I'll being acquiring the necessary background on computer design and operating system theory.

This phase will end up with specifications for the hardware design.

[End Date: 06/01/2009]

Phase 2: Hardware Design Phase 2: Hardware Design

Start Date: 06/02/2009

This phase will end up with a complete and detailed design of the machine's hardware.

Phase 3: Construction Phase 3: Construction

This phase will end up with a functional machine with no software support. Code will be entered into memory by hand using the front panel switches. No signs other than LEDs will exists.

Phase 4: Experimenting with short routines Phase 4: Experimenting with short routines

The machine built in Phase 3 will serve as a laboratory for testing different software approaches, entered by hand using the front panel switches.

Phase 5: Peripherals Phase 5: Peripherals

At least one peripheral will be added to the machine for dumping code into memory. I am thinking of a RS232 port but this may change. Being able to dump large amount of code into the machine will allow me to experiment with more sophisticated code. This code, however, will still being assembled by hand.

Phase 6: Assembler Phase 6: Assembler

The manufacturing of development tools starts with this phase. I will be writing an Assembler. The purpose is to initiate my self into this specialized area and to gain experience for further development. Besides, I will need an assembler any ways.

This phase will end up with an Assembler capable of generate machine code for my computer.

Phase 7: Research on OS Phase 7: Research on OS

In this phase I will be experimenting with development tools such as retargatable C compilers and trying to understand Opens Source Kernel's C code. I am supposed to have a good understanding of operating systems principles from Phase 1, so this is the time to put some hands-on.

At the same time, I will had gained sufficient experience with Linux and its development environment and tools. Must likelly I will be writting software using a Linux computer rather than a Windows one.

This phase will end up with a decision about what operating system to adopt. I am thinking of Minux or other UNIX-like OS but this may change.

Further Further

New phases will follow but this is not the time to anticipate it.

|