External ArchitectureUnits

The Heritage/1 minicomputer consists of several units. Each unit is a rack-mount multi-cards frame with its own power supply and internal buses. Different configurations are possible by combining different units in a number of possible ways. They can all populate a single rack or arranged in different ones as needed.

Units communicate each others by the mean of a 39-lines bus called U-BUS. Externally the bus consists of two cables ended with D-SUB connectors (37-pins and 9-pins respectively). Cables plug to units in a daisy-chain fashion. The last unit in the chain requires to be terminated by the mean of a two terminator connectors.

Wires in the bus carry either signals or ground. No power is provided through the U-BUS.

Console

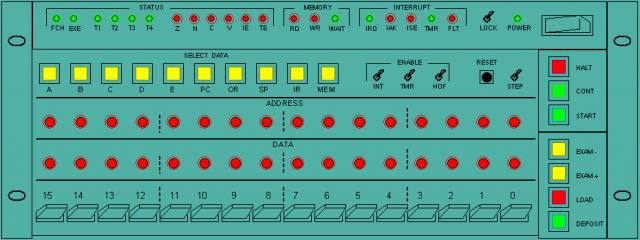

The Console, possibly the most prominet component of the machine, is placed on the front of the Central Processing Unit (CPU) which is in turn the most important unit on the entire computer.

The Console is used for operating the machine and also for debugging developing software. It relies on five boards to function; one (H11R-LARLDR) plugs to the Backplane along with the rest of CPU cards; the other four (H11C-CONC, H11D-CONB and two H11D-CONL) are located within the Console assembly.

As a whole, the Console is considered a "controller" as it runs sequences on its own in response to commands issued by the Operator from the Console's buttons and switches. Know however that Console sequences can only run when the computer is in Halt mode, as explained in the Operator's Manual.

Main Memory

Main memory is located in a dedicated unit called "Core Unit". Modern memory chips occupy little space but further expansion is expected (such as building ROM based on diodes-matrixes, support for Virtual Memory etc.) hence the extra space needed.

Memory is wired in 16-bits words (as opposite of 8-bits bytes). This means that a given address allways referres to a memory location which is 16-bits wide. A number of instructions have been provided for manipulating bytes within words but that is only once the content has been read into a CPU register.

At present, the 64 Kwords addressable space is "real", that is no support for Virtual Memory yet exists.

Peripherals

Peripheral's controllers are built as Units. For example, the "COMM Unit" contains a number of UARTs for RS-232 ports accessible from its rear panel. Different controllers can be housed within the same Unit for convenience. For example, an IDE hard drive could be placed in the COMM Unit in order to save space.

In Heritage/1, all peripherals are memory mapped. This implies that device's registers and buffers occupy a portion of the overall (64 Kwords) addressable space. These memory chips (wired as dual-port memory) and associated circuitry reside in the peripheral's Unit. The address range is manually set by the mean of DIP switches located in the unit in question.

Expansion

The Heritage/1's topology puts no limit to expansion. New units can be designed, built and added to the existing configuration as required.

An interesting area for expansion is Virtual Memory. Originality the machine does not provide any support for that; however, it can potentially be implemented in the Core Memory Unit without having to modify the CPU at all.

Detailed information and guidance for designing new Units are provided in this Manual.

|