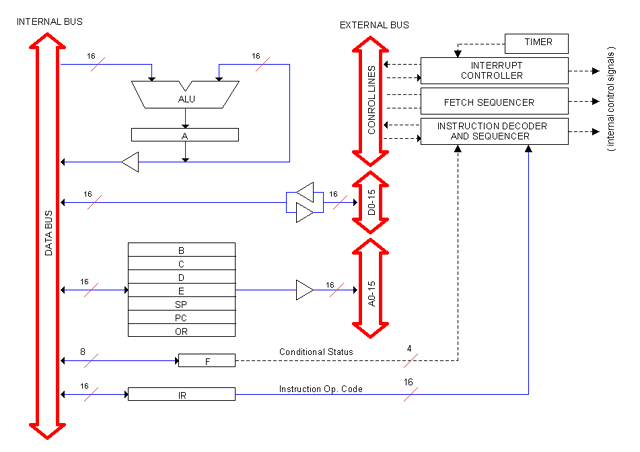

Block Diagram

CPU registers are grouped (for better understanding) into these categories:

- General Purpose (B, C, D, E)

- Special Purpose (A, PC, SP)

- Hidden (IR, OR, F)

- Console (LAR, LDR, SW)

All of them are 16-bits except F, the Flags register, which is 6-bits.

Registers communicate each others throughout two internal buses: Data Bus (D-BUS) and Address Bus (A-BUS, which is not shown in the diagram for simplicity). General purpose registers can read from the D-BUS and write to both. Special registers PC (program counter), SP (stack pointer) as well as the hidden register OR (operand register) can also read from the D-BUS and write to both.

The purpose of this arrangement is to allow indirect addressing from any of the general purpose registers. For example, an instruction making use of E as a pointer to memory will make it to write its content to the A-BUS.

The operand register (OR) is the destination for the operand during an Operand Fetch Cycle. For immediate addressing instructions, the operand is an immediate value; during the Execution Cycle, OR will write to the D-BUS. For direct addressing instructions, the operand is an address; during the Execution Cycle, OR will write to the A-BUS.

The External Bus consists of 16 lines for Address, 16 for Data and 7 lines for Control. It connects with internal buses throughout 3-state buffers as shown.

Register A is the "accumulator". The block diagram shows A in mutual relationship with the ALU. In fact, the accumulator is the only destination for ALU operations; it can also be used as a general purpose register with the only limitation that it can not write to the A-BUS so it cannot be used as a pointer to memory.

The Flags Register (F) contains four conditional status flags: Zero (Z), Negative (N), Carry (C) and Overflow (V). Two Additional bits hold the status of Interrupt Enabled (IE) and Timer Enabled (TE) conditions.

All Flags are set or reset using dedicated lines not shown in the diagram. Additionally, the Flags register connects to the D-BUS so it can be saved and restored to/from the Stack during CALL instructions or Interrupts.

Console registers (LDR, LAR and SW, not shown in the Blog Diagram) are managed by the Console Controller. SW is actually a 3-state buffer to the D-BUS. LAR and LDR output directly to the ADDRESS and DATA Lamps displays (respectively) located in the Console's front.

All CPU internal control signals (except those for Console registers) are generated in a circuit called Instruction Decoder and Sequencer (IDS, actually built with more than one card). The IR register output goes directly to this circuit to provide the current instruction code being decoded and executed.

Sequences for Op. Code Fetch and Operand Fetch cycles are generated by a separate circuit called "Fetch Sequencer". Interrupt sequences are built separately by the Interrupt Controller card.

Synchronization between controllers (Fetch Sequencer, IDS cards and Interrupt Controller) is assured by Status signals S0,S1 and Sequence Encoded Time ET0, ET1 generated by a Master Controller card. This card also contains the Flags register (F), the Master Clock generator and some other important circuits.

A Timer circuit interrupts the CPU at regular intervals for providing the "computer's tic". This can be enable or disable both from software and from the computer's Console.

|

Homebuilt CPUs WebRing

JavaScript by Qirien Dhaela

Join the ring?

David Brooks, the designer of the Simplex-III homebrew computer, has founded the Homebuilt CPUs Web Ring. To join, drop David a line, mentioning your page's URL. He will then add it to the list.

You will need to copy this code fragment into your page.

Project start date: May 13 of 2009

|