Phase 2: Hardware DesignDecision-Making and Testing

My Spec is (intentionally) open so I'm now before a wide spectrum of decision-making challenges such as: What kind of components to use (TTL/CMOS, FPGA), going RISC or Microcode, whether to plan or not for Superscalar, Cache... that kind of things.

Obviously the only I can do is to tackle things one at time. Actually, each little part of the CPU circuitry (registers, ALU, Sequencer, etc) constitutes a whole World to me due my profound ignorance about these topics. It is truly difficult to make decision about things that you don't know well, but that has been my challenge since this project started.

Microcode or Hard-wired Logic?

06/03/2009

My first focus of attention has been the Instructions Decoder and Sequencer.

It seemed at first that Microcode is the only way to go. However, a quick research via Internet showed me that such decision is far from obvious, though very attractive indeed.

Microcode presents irresistible advantages to me:

- Easy to understand

- Easy to implement

- Naturally extensible

But it also has a disadvantage: It can get inefficient compared with other options such as a RISC-like hard-wired logic implementation, specially if one goes creative and build long, complex instructions. My computer will be slow for sure so I am almost obligated to compensate for that with efficiency.

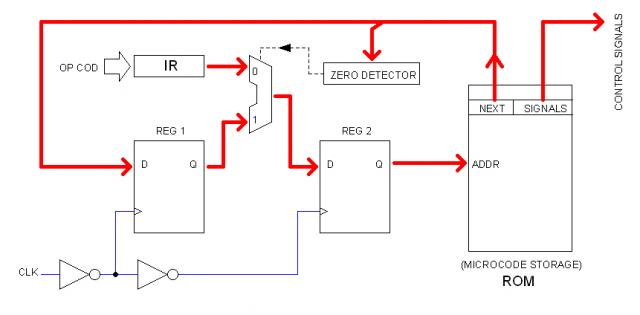

Nevertheless I sketched a block diagram of what it would be my Microcoded Sequencer (I prefer to call it FSM since that's what it is basically). Here it is:

A brief explanation of the diagram is in here.

The other way is hard-wired Logic... which is not obvious either.

I had established that my op code is 16 bits. That is because my computer has the traditional Von Neumann architecture so data words and code words are the same width. I don't really know if there is sufficient room for field-oriented instruction encoding in 16 bits; that is something that I would need to explore.

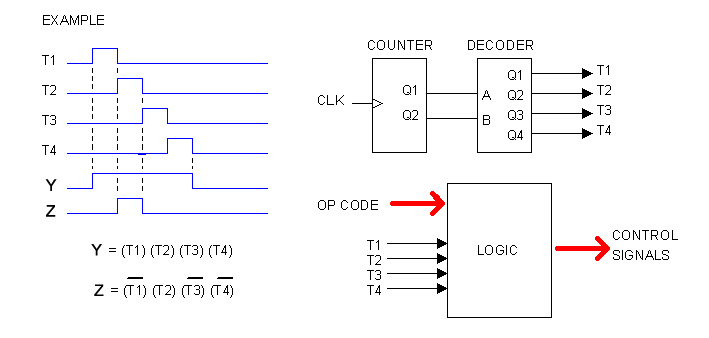

Nevertheless I also asked my self how to decode without microcode and came with this approach:

For an explanation on how it works, click the link below:

index.php?branch=155

The fact of the matter is that I can't make a decision yet. Perhaps it is better to left this matter for later, when I had advanced the design of the CPU circuitry thus I had a better idea of what control signals I really need to produce.

Considering PLDs

06/03/2009

It is all about density. If I wanted to build a "pocket computer", I'd surely picked FPGAs. But I want my computer to be bulky, as in the old days. However, employing only SSI/MSI chips would make it "too bulky". That's why I'm turning to what is in between: PLDs, or actually a mix of PLD/SSI/MSI.

Moreover, FPGA portraits important constraints to me. To start with, I'm determined to use the traditional (and cheap) 0.100 inches prototyping boards, so I need all components to come in DIP packages. Adapter boards exist but they are prohibit to my budget.

Another problem that I see with FPGA is modularity. Being them so dense, I would be tempted to encapsulate large amount of logic in a single chip. Indeed I can always make changes to the firmware but that is not the kind of "modularity" I seek; it is not being able to start from scratch each time, but instead to be able to change one part without impacting others.

I started to explore PLDs today. ATMEL ATF22V10C, for instance, seems perfect for the "hard-wired" CPU Sequencer that I was picturing yesterday, no more, not less. I am thinking in those kinds of blocks and that kind of density.

The first step into reality

06/06/2009

From paper to the breadboard. Today the Heritage/1 putted the first leg on a tangible World. Like an embryo starting to take shape into the mother's belly, something like that. I'm very exiting.

Yes, I did the first breadboard test today. For details, follow this link:

index.php?branch=163

The test was really trivial but it gave me the necessary confidence. I have worked with logic circuits before; I have worked with microprocessors (8085, Z80) and Microcontrollers (PIC) as well. But building a computer without a microprocessor is totally new for me.

So today the project entered a new momentum in which I'll be designing and testing the building blocks of the Heritage/1: Registers, Multiplexers... From now on, everything is real.

Heritage/0 ?

06/11/2009

Early in the morning, a surprising idea came suddenly to my mind. A "pre-project": a computer prior the Heritage/1.

I was thinking that the things I need to test now (and before testing, design and build) are so very elementary that the overall prospective of a computer such as Heritage/1 is not actually needed. In other words, I don't need to test "the building blocks of the Heritage/1" but instead "the building blocks of a computer" (any).

And the surprising idea that came to my mind soddenly this morning was to put those blocks together to build a simple, very elementary computer. No Pages Tables, no "Matrix", no Supervisor Mode. No Operating System either (not now, no ever). Just the chance to peacefully concentrate in the very elementary building blocks that any computer of this kind needs to have, such as registers and buses, memory and interface with peripherals.

I think is a reasonable idea... I will consider it.

|