ContentHeritage/1 is (or will be) a basic 16-bits homebrew minicomputer built with the purpose of learning the basis of computer design in an intimate way. However, I'm aimed to produce a machine reasonably fast and capable of doing some useful work.

The Project

This project is about designing and building Heritage/1, an old-fashioned homebrew minicomputer similar to those in the latest 60's and early 70's. Official start date is 05/13/2009. Completion is expected within one or two years from the starting date.

A love story

While searching the Internet for "relay computers" in May 2009, I discovered the world of "Homebrew CPUs" and got fascinated with the idea. Determined to build my own old-fashioned minicomputer, I commenced to study existing projects as well as building, little by little, a basic background on computer design and OS development.

One month later I had a total mess of ideas and a loved creature called: the "Heritage/1" homebrew minicomputer. Soon I realized that the project was too complex for a first try so I decided to put it on hold while devoted my efforts to a simpler "pre-project" that I called "PREHER/816". This would be a simple 8 bits machine resembling the architecture of a Z80 microprocessor; the purpose was then to gain the necessary experience for tackling the "main project" (Heritage/1) in a second step.

However, the ideas developed during the "pre-project" resulted interesting enough to me so I started to fall in love with the new computer up to the point that I decided to make her the main subject of my project and that's how she inherited the name reserved for the previous one: Heritage/1. Eventually the project evolved into an even simpler machine based on a quasi-ortogonal 16-bits architecture pretty much inspired by John Doran's D16/M minicomputer.

As a result of all this going back and forward, you will see mixed names in this web site. For now, Heritage/1 refers to the current machine being designed.

Heritage/1 is now meant to be simple and fast (as fast possible for the old technology it employs) and it is for the sake of speed that microcoding has been discarded at once and data transfer is being engineered so it takes the shorter path possible.

So Heritage/1 is (or will be) a simple 16 bits home-brew minicomputer and it is that (simplicity) the most loved feature that I find in the design being developed.

What can we expect from Heritage/1?

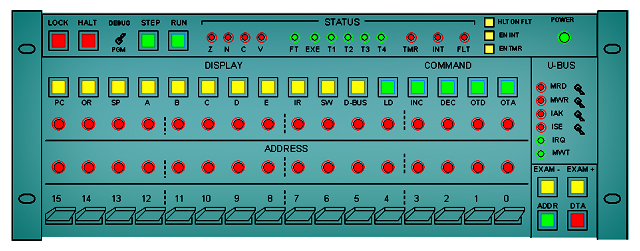

Heritage/1 is expected to resemble a minicomputer similar to those of the 1970's. It won't feature the nowdays familiar video monitor, keyboard and mouse but the "clasical" switches and lamps (LEDs) on the prominent Control Panel.

At the beginning there will no Operating System so the machine will be some kind of laboratory for experimenting with low level software. Storage will appear at some point; I wish to employ magnetic tapes but that would be tremendously expensive, so must likely it will an IDE hard drive, a Floppy Drive or something similar.

Hopefully a "Monitor" program (a rudimentary operating system) will be developed at some point in history so users will finally be able to run "useful" programs. Users will access the computer from PCs running terminal emulation applications such as Hyper Terminal, connected via RS232 ports. They will also be able to connect remotely through the telephone line via modems as in the old days.

As per applications, I am not thinking in word processors or spread sheets, but Mathematics oriented programs most likely running in a batch-processing fashion. Database applications are also feasible.

Multi-tasking and multi-users, that is, a "real" operating system is far away if ever happens at all. Nevertheless, Heritage/1 is open to any kind of software experiments with the advantage of having a hardware very well known up to the last screws and nuts.

Project Status

12/01/2010:

This project can be traced back to May 2009 but it actually started to take shape on July 2009 when I adopted the 16-bits double-buffer architecture that finally survived. That was one year and five months ago. More that one thousand dollars have been spent since then in components, connectors and prototyping boards... very expensive stuff for a poor individual such as my self!

Most of the circuits have been drawn, some have been built and tested and a mountain of ideas about system software and applications has grown little by little, but only on paper because there is not way for testing them until the hardware is ready. An assembler (H1ASM) and a simulator (H1SIM) were developed in Borland Turbo Pascal 3 using an old MS-DOS PC.

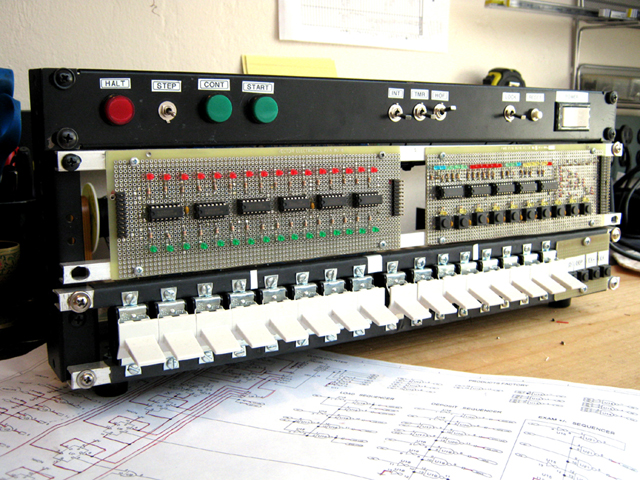

What I was trying to build is a "lab implementation" of the CPU. The Console and most of their support boards were built and tested. The project was going well but slowly... very slowly: estimates showed me that it would take another year (at least) for completion.

On 10/13/2010 I made the difficult decision to put the project to sleep until I could find enough spare time in my busy life. I then started a simpler project termed LC-81, based on Zilog Z80 microprocessor instead of discrete logic.

I've started to post notes in the following site:

http://www.armandoacosta.com/lc81

The Computer

Heritage/1 is a homebrew minicomputer featuring an architecture similar to those of the 1960's and 1970's. It uses the 74HC series of SSI/MSI integrated circuits. It also uses SRAM chips being those the only LSI ones employed. Not even ROM chips has been considered in the design althougth some little programs may reside in "read only memory" made out of fast-switching diodes, that is a (manually programmed) diodes-matrix.

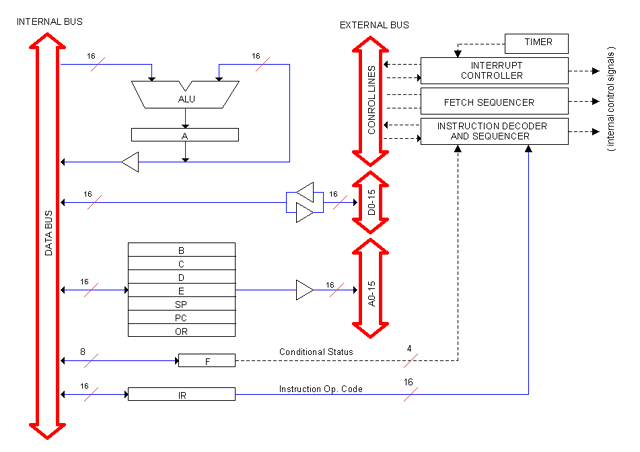

Most registers in this computer are built using presettable up/down synchronous counters. This allow registers to be incremented or decremented in a single clock period without data transfer or ALU usage involved. General purpose registers are also double-buffered so they can write to either Data or Address bus making indirect addressing very simple.

The computer is strictly 16 bits meaning that Memory is organized into words, not bytes. The 16-bits Address Bus can directly address up to 64 Kwords of memory (or 128 KB if you prefer to count it that way).

Instructions are decoded by hardwired logic, that is using boolean algebra instead of microprogramming. This is both interesting and eficient.

A Timer circuit provides a "computer tic" to produce a cylclic interrupt. This may be used by an operating system for scheduling different processes in a multiprogramming fashion.

Construction

The Heritage/1 minicomputer will consists of several rack-mount "units" such as the CPU, the Memory Unit, the Comm Unit and others, housed in a 19-inches industrial rack possibly 20RU high. An external bus called U-BUS connects all units together whereas each of those possess its own specific internal bus.

The CPU in particular is housed into a multi-cards frame. Cards are built using 8x5.5 inches prototyping boards that plug to the frame's Backplane.

The CPU Backplane consists of 96-pins and 120-pins DIN 41612 connectors conveniently wired into different interal buses. Some complex circuits such as the Instructions Decoder and Sequencer (IDS) expand among several cards.

CPU Block Diagram (simplified)

Summary

Data Bus : 16 bits

Address Bus : 16 bits

Main Memory : Up to 64 Kwords

Arithmetic : Signed integer (two's complement)

Inst. decode method : Hard-wired logic

General Purpose regs: B, C, D, E: 16 bits double-buffered to Data and Address buses

Special Registers : A, PC, SP : Accumulator, Program Counter and Stack Pointer

Hidden Registers : IR, OR, F : Instruction Reg, Operand Reg and Flags register

Console Registers : LAR, LDR : Lamps-Address and Lamps-Data registers

Real-Time Timer : 1 ms "computer tic".

Peripherals : Memory Mapped

Interrupts : 64K External Interrupts plus 256 vectored Internal Interrupts

Technology : SSI/MSI HCMOS chips

Construction : Prototyping boards housed in rack-mount multicard frames.

Clock Speed : 4 MHz

Addressing Modes

Register : Data is contained in given register.

: mov a, b ; A=B

Immediate : Data if given in the word following the op. cod (operand).

: movi a, data ; A=data

Direct : Data is in the memory location which address is given in the word following the op. cod. (operand).

: ld a, addr ; A=[addr]

Indirect : Data is in the memory location which address is contained in a register used as a pointer.

: ldx a, d ; A=[D]

Relative : (Branch only). Jump to OFF_SET relative to current instruction address. The OFF_SET if given as an operand.

: jnzr OFF_SET ; PC=PC+OFF_SET

Relative Indirect: (Branch only). The OFF_SET is the content of given register.

: jnzrx d ; PC=PC+d

Stack : Data comes from the Stack which is always pointed by register SP.

: pop a ; A=[SP]; SP=SP-1

Interrupts

The Heritage/1 interrupt architecture allows for 64K interrupts which priorities are determined by the hardware topology. Three control lines are present in the External Control Bus: IRQ (Interrupt Request), IAK (Interrupt Acknowledge) and ISE (Interrupt Services End). These lines are connected to all devices in a Daisy Chain fashion so any interrupter device can open the lines to avoid further propagation along the chain. This way, priority gets establiched by the "proximity" of the device to the CPU.

Peripherals

We call "peripheral" to any device that is external to the CPU. Included in this group are: the Main Memory, the COM Ports, the Tape Drive Controllers and many others. All of them are mapped within the same addressable space.

Some peripherals (notably, Terminals) connects to the CPU via RS232 ports. Most others, however, are attached to a common external bus that we call "U-BUS" consisting of 16 data lines, 16 address lines and 7 control lines.

Peripherals contain their own memory chips allocated in designated addresses. These are wired as dual-port memory so both the CPU and the peripheral circuitry can read/write from/to them. Typically, a status register and at least one-word data buffer are implemented per peripheral.

A typical communication between the CPU and a device runs like this:

The CPU sends a command to the device by writing the device's status register. For the CPU prospective it only had wrote a word to a memory cell. The CPU does not wait for the response but it keeps working on something else.

The Device reacts to the command doing some work. Say for instance that it gets data from the magnetic tape to fill in its internal Buffer.

When the Device finishes, it interrupts the CPU which, in response, reads the Device Buffer into Main Memory. Possibly this cycle repeats several times until the desired amount of data is read into Main Memory.

The Web Site

How to navigate this site

It's easy to get lost in this web site if you think of it as a web site, because it is designed more like a collection or "books".

When you enter a "book" you see a Table of Content (TOC) which is organized as a tree. When you click a TOC entry, you get to the entire branch (from that point down) presented as a book chapter. So it is opt to you to watch the entire book, part of it or to focus in a single record.

Once in branch view, you can use the TOC link to return to the Table of Content or you can use the Step-Up link to navigate the tree backwards (one step back). You can also click on a title to navigate the tree forward (narrow).

If you plan to print from this site, use the "Print View" link. It will take you to a non-web-looking version of the branch you are visiting. If you happen to be in the TOC, then the whole book will be presented. Actually, this is the only way of watching the entire book at once.

Finally is the "Search Box". The search engine is quite primitive: if finds records containing the keyword you entered as a substring of either its title of its content. For example, if you are looking for "homebrew computer" you can enter "homebr". In the resulting list, books are highlighted in bold. Search is case insensitive.

Binary download is not implemented yet but it will be soon.

How the site was developed

This site was written with PHP, based on a generic library I developed some ago, called "Help Books". It relies on a MySQL database which structure is very simple: records are defined to be "nodes" of a unique tree; "Books" are actually nodes which parents happen to be the root of the tree.

Help Books had proven to be a convenient technology since it allows for easy rearrange of the content. In fact, moving entire branches (even across books) is very simple from the code prospective. The hierarchical organization of the content, on the other part, is very natural for technical documentation such as that for this project in particular.

As a consequence of the flexibility provided by Help Books technology, this site is in constant change, not only because new content is added frequently but also because existing content is being rearranged in favor or organization. The site you are visiting right now might be very different from what it was months ago.

Nevertheless what you are visiting now is the most recent and convenient view of a huge amount of content built little by little along months of documentation effort, and is still growing and reshaped conveniently as the project evolves.

|